# A Simple Computer Design

- ◆ Determine hardware requirement in design of a simple computer

- ♦ Discuss use of Register Transfer Language in computer design

- Design control unit of a simple computer

- Discuss how to program the simple computer in solving various problems

In this chapter, we demonstrate how the knowledge that you gathered in this book can take you to the next higher level, where you can start designing a digital computer. A digital computer is capable of computation and taking decision based on binary coded instructions stored inside it. The central processing unit (CPU), also known as the brain of the computer sequentially fetches these instructions, decodes it and then executes it by performing some action through available hardware. In this chapter, we'll design a simple computer, which has a limited instruction set but is capable enough to solve variety of arithmetic and logic problems. The technique you learn in developing this simple machine will be useful when you go for a full-fledged computer design in some higher-level courses.

We begin the chapter by defining a small problem, which our simple computer should be able to solve. Next, we spell out different hardware components required as building blocks. We'll also discuss a simple hardware operation description language, called Register Transfer Language (RTL) useful for state machine design. Through RTL we'll describe all the operations of our simple computer. Then we'll design the control unit that will coordinate all these operations. Finally, we will discuss how to program this simple computer to solve the problem we started with and many other arithmetic and logic problems.

## 16.1 BUILDING BLOCKS

In Section 1.6 of Chapter 1, we have broadly seen the kind of components required for designing a computer. In this chapter, we address how to design central processing unit of a simple computer that interacts with a small memory module. Before we proceed further let us define a problem that our computer is supposed to solve. This is not the only problem it can handle. Depending on how we program it, we will be able to solve different arithmetic and logic problems and that is shown towards the end of this chapter through examples. The purpose of defining a problem is to choose specific hardware components that will serve as building block of our simple computer.

#### The Problem

Add 10 numbers stored in consecutive locations of memory. Subtract from this total a number, stored in 11th location of memory. Multiply this result with 2 and store it in 12th location of memory. All the numbers brought from memory lie between 0 and 9.

#### Memory

Since, the problem says the numbers or data to be fetched from memory and we also know that programs, i.e. binary coded instructions are also stored in memory, let us divide the memory used in our computer in two parts. One part stores the program or series of instructions the computer executes sequentially and this is known as *program memory*. The other part houses data that program uses and is also used for storing result. This is called *data memory*. From the given problem we find, we need 12 memory locations for data storage. We expect our computer won't need more than 20 instructions to complete the given task hence, a memory with 32 locations (integer power of 2) can be selected for our computer.

Now we try to decide how many bits of information we store in each address location. Usually, bits in memory locations are stored in multiple of 8 called *byte*. Let's see if our job can be done with 8 bits. Each memory location stores data between 0 and 9 on which program operates and thus require only 4 bits. The final result at most can be  $10 \times 9 \times 2 = 180$  which requires 8-bit for representation. So the data memory can be of 8-bits with which we can represent decimal number up to  $2^8-1=255$ .

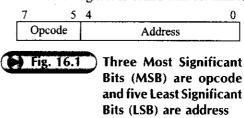

Let's now see the requirement of program memory. There, in each location, certain number of bits are allocated that defines the instruction to be executed. This is called operation code or in short, *opcode*. The rest of the bits can be used for referring the memory location from which data is to be brought or stored, if required by the instruction. Since, 32 memory locations require  $\log_2 32 = 5$  bits for memory referencing we'll have 8 - 5 = 3 bits for opcode specification giving  $2^3 = 8$  different opcodes (Fig. 16.1). We'll see that 8 instructions are sufficient for the given kind of task in our limited ability computer. Hence, one important hardware component of our computer gets decided. The memory to be used is of size  $32 \times 8$ .

The above mode of addressing memory for data is called *direct addressing*. If the address mentioned in the instruction contains address from which actual data is to be brought it is called *indirect addressing*.

If after opcode, in place of address actual data is made available, it is called *immediate addressing*. Note that, in immediate addressing data cannot be more than 5 bits as 3 bits gets used in opcode. Also note that the instruction like this is called single byte instruction. If an instruction requires 2 bytes to be fetched from program memory it is called 2-

byte instruction. Obviously, in 2-byte instruction number of opcodes or memory addressing capability can be more than a single byte instruction.

## **Register Array**

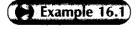

The computer needs a set of registers to perform its operation. Let us define them and assign task to each one of them for our simple computer. Note that, we are using a  $32 \times 8$  memory module.

Memory Address Register (MAR) is a 5-bit register that stores the address of the memory location referred in a particular instruction. The output of this is fed to a 5-to-32 address decoder. Each output of the decoder points to a location in the memory. All memory referenced instruction loads memory address in MAR.

Memory Data Register (MDR) is an 8-bit register that stores the memory output when a memory read operation is performed. During memory write operation it stores the value that gets written to the memory. Thus it can also be called a memory buffer. In arithmetic or logic operation when more than one operand is required by ALU, one operand in our simple machine comes from MDR.

Program Counter (PC) is a 5-bit counter that stores the address of the memory location from which next instruction is fetched. At power on, our machine PC is reset so that its content is all zero. Thus location 00000 has to be a part of program memory and this is also the starting address from which program execution begins. Since, in our simple machine all the instructions are single byte instruction, every time an opcode is fetched we'll increment PC by one, and thus PC will point to location of the next opcode.

Instruction Register (IR) is a 3-bit register, which retains the opcode till it is properly executed in one or more clock cycles. Since all memory read and write operations are done through MDR, after an instruction is read from memory, 3 MSB that contains the opcode are transferred to IR.

Accumulator (ACC) is a multi-purpose register that always stores one operand of an arithmetic or logic operation. The result of this operation, i.e. ALU output is also stored in ACC. Functions like shifting of bits to left or right are also carried on ACC. Thus, in our simple computer ACC is a shift register with parallel load facility.

Timing Counter (TC) is a synchronous parallel load counter that stores and updates the timing information. The timing counter output is decoded to generate different timing signal, which in turn triggers different events in execution of an instruction. The counter is reset synchronously with clock once an instruction is fully executed. If an instruction is conceived as a macro operation then series of sequential steps necessary to carry out the instruction in the computer is called micro operations. In our simple computer, we are not expecting more than 8 micro operations for any macro-operations and hence a 3-bit counter is sufficient. Later if we see, we need more than 8 micro operations we'll change it to a 4-bit counter. Note that, a master clock (also called system clock) to which all the state changes of the computer are synchronized, triggers this counter. Also note, TC has power on reset facility, i.e. when the computer is switched on it stores 000.

Start/Stop Flag (S) is a flip-flop which when set, stops execution of the program. This we do in our simple computer by inhibiting the master clock. Like program counter, this also has a power-on-reset facility so that when the computer is switched on the master clock is not inhibited.

#### Other Important Hardware

Arithmetic Logic Unit (ALU) is a versatile combinatorial circuit that can perform a large range of arithmetic and logic operations. Since the data is 8-bit long, we use an 8-bit ALU. The control input value decides the function ALU executes at a particular time. ALU can accept up to two operands at a time, one from ACC and the other from MDR. The ALU output is stored in ACC. If addition operation generates a carry output from ALU, that can be stored in a flip-flop, often called carry flag (CY). Since, in our problem numbers are small in

magnitude the 8-bit ALU doesn't generate carry output and we don't need CY flag for our simple computer. Note that, ALU cannot perform multiply and division operation for which we use special hardware or some indirect technique.

Instruction Decoder (ID) is a 3-to-8 decoder, which takes input from IR and thereby decodes the opcode. In our simple computer there are 8 different opcodes, each one making one of the decoder output  $(D_0, D_1, ..., D_7)$  high. This in turn initiates specific micro operations necessary to execute that opcode in subsequent clock cycles.

Timing Sequence Decoder (TSD) is again a 3-to-8 decoder that takes input from TC and provides necessary timing information in the form of decoded output  $(T_0, T_1, ..., T_7)$  for a micro operation to be executed.

BUS is a group of wires that serve as a shared common path for data transfer of all the devices connected to it. With this, we do not need a separate device to device connection which increases the number of wiring specially when large number of devices are used in a system. Since, the largest group of binary data that is transferred in our computer is 8-bit, the bus used is an 8-bit bus.

BUS Selector (BS) is a multiplexer, which decides which one of all the connected devices is in transmission mode, i.e. has placed data in the BUS. Note that, if more than one device try to send data simultaneously, there will be a conflict producing erroneous result. However, in our computer we may allow more than one device connected to BUS to receive data from BUS. We'll see shortly that only *PC*, *ACC*, *MDR* and ALU want to transmit or place data on the BUS. *MAR* and *IR* only receive data and other hardware give control signal and don't do data transfer. Thus, BS has to select one of the four devices and uses eight (each one for one bit) 4-to-1 multiplexer type of device. We can also use tri-stated output for bus connection (Section 14.6 of Chapter 14) that will reduce the current loading on the device when it is not selected.

From this discussion we can draw the *data path* of our simple computer as shown in Fig. 16.2. Here, by data we mean address, opcode as well as operand and they move from/to memory, register, ALU, etc. Of course, we need another set of path to send control signal to various hardware to carry out microoperations. This is called *control path* and we'll design it when we define the instruction set for our computer.

Generally speaking, address bus is the group of wires that transfer address information, data bus is another group that transfers data and control bus transfers control information. Often, address information and data are transferred through a common bus and a control logic decides which is to be transferred and when. You might have noticed that in our simple computer design, we have used a common address and data bus. More about control bus will appear in Section 16.4 where we discuss the design of control unit.

Find in Fig. 16.2 the direction of arrow that shows the direction of data flow. Note that, IR and MAR can only receive data from BUS; PC can only send data by BUS; ACC and MDR can do both;

Memory data transfer takes place only via MDR and operands of ALU come from ACC and MDR and result is sent via BUS.

In a particular configuration each memory location contains 16-bit data. In program memory, if 4 MSB contains opcode and rest contains address of memory locations give (a) Number of opcodes (b) Size of memory (c) Size of *PC*, *IR*, *ACC*, *MAR* and *MDR*.

#### Solution

- (a) Number of opcodes =  $2^4 = 16$  (Maximum)

- (b) Number of address bits = 16 4 = 12. No. of memory locations =  $2^{12} = 2^2 \cdot 2^{10} = 4$ K. So size of memory is  $4 \times 16$ .

- (c) Size of PC and MAR = No. of address bits = 12. Size of IR = Size of opcode = 4. Size of ACC and MDR = No. of data bits = 16

Fig. 16.2 Data path of the simple computer

SELF-TEST

- 1. What is the highest integer in decimal that we can store in 16-bit data field?

- 2. What is an opcode?

- 3. What is the function of program counter?

- 4. What is indirect addressing?

#### 16.2 REGISTER TRANSFER LANGUAGE

Before we go for design of control path and the control unit as a whole we have to define macro operations and then we need to break up each macro operation in series of micro operations at register level. Register Transfer Language (RTL) gives a simple tool through which these micro operations can be expressed and then control unit can be designed from that. The basic structure of this language is

$$X: A \leftarrow B$$

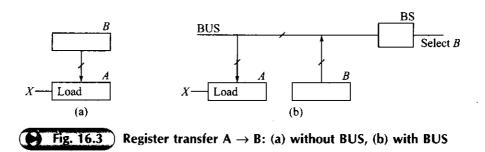

This means, if condition X is TRUE, i.e. X = 1 then content of register B is transferred to register A. X can be a single logic variable or a logic expression like  $xy \equiv x \& y$ ,  $x + y \equiv x | y$ , etc. In RTL we distinguish logic operation 'OR' from arithmetic operation 'addition' by assigning symbols ' | 'and '+' respectively. The logic AND is expressed by symbol '&'. However, if the '+' sign appears left to ':' in an RTL statement it means logical OR and '.' refers to logical AND. This is so because to left of ':' only logical operators can reside. Often AND, OR, NOT are expressed by 'A', 'V', '~' respectively. Also note, this register transfer destroys the previous content of A but not that of B. Both the register A and B now have the same value. If register transfer takes via BUS

$$A \leftarrow B \equiv BUS \leftarrow B, \quad A \leftarrow BUS$$

Since, BUS is not a register but a group of wire this means B getting access to BUS through BUS selector (BS) and the whole event takes place in one clock cycle. Figure 16.3 pictorially depicts register transfer without and with BUS.

To write anything to memory, in our simple computer we have to place the address information in MAR and the data to be written in MDR. Thus, memory write operation in RTL is expressed as

$$X: M[MAR] \leftarrow MDR$$

Similarly, memory read operation is also done through MAR and MDR and RTL expression is

$$X: MDR \leftarrow M[MAR]$$

If certain bits of a register are to be addressed we use RTL as follows:

$$X: IR \leftarrow MDR[7:5]$$

The statement above refers to transfer of three most significant bits of MDR to IR, a 3-bit register when X = 1.

The arithmetic and logic operations of ALU that bring operands from ACC and MDR and store the result in ACC can be expressed in RTL in the following way

| $X: ACC \leftarrow ACC \& MDR$     | [logic AND]              |

|------------------------------------|--------------------------|

| $X: ACC \leftarrow ACC \mid MDR$   | [logic OR]               |

| $X: ACC \leftarrow ACC \oplus MDR$ | [logic EX-OR]            |

| $X: ACC \leftarrow ACC'$           | [logic NOT]              |

| $X: ACC \leftarrow ACC + MDR$      | [arithmetic addition]    |

| $X: ACC \leftarrow ACC - MDR$      | [arithmetic subtraction] |

| $X: ACC \leftarrow ACC + 1$        | [increment by 1]         |

| etc.                               |                          |

And finally if data is to be shifted in a register say by 1 bit to left we can write

$$X: ACC[7:1] \leftarrow ACC[6:0], ACC[0] \leftarrow 0$$

If such left shift occurs through carry the statement will be

$$X: ACC[7:1] \leftarrow ACC[6:0], ACC[0] \leftarrow CY$$

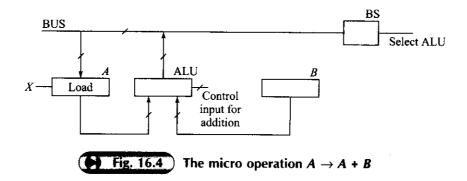

Normally, we come across these four kinds of micro operations namely (i) Inter-Register transfer (ii) Arithmetic operation (iii) Logic operation and (iv) Shift operation. Note that, left shift without carry can also be obtained by addition operation as shown in Example 6.14 of Chapter 6. Figure 16.4 shows how addition operation  $A \leftarrow A + B$  takes place through ALU and BUS.

Note that, TC and PC can increment by 1 without taking help of ALU as they are designed to be parallel load up counters. For more complex processor unit where 2 byte, 3 byte instructions are possible we can have an adder unit accessible by PC.

## Example 16.2

Explain what the following RTL statements perform

$T_1: MDR \leftarrow ACC$   $T_2: ACC \leftarrow ACC'$  $T_1: ACC \leftarrow ACC \& MDR$

Solution The first statement says if  $T_1 = 1$ , content of ACC is transferred to MDR. The second statement says if  $T_2 = 1$ , content of ACC is complemented. The third statement says if  $T_3 = 1$ , bit-wise AND operation is performed on ACC and ACC and the result is stored in ACC. Since content of ACC were complement of one another before this statement is executed, by AND operation all the bits of ACC become zero, i.e. ACC is reset by these three statements irrespective of its initial content.

Note that,  $T_1$ ,  $T_2$  and  $T_3$  can be output of a timing sequencer, which become active one after another in consecutive clock cycles. This way, ACC can be cleared in three clock cycles by above RTL statements.

5. What is RTL?

and the property of the series

6. What is to be changed in Fig. 16.4 to perform  $A \leftarrow A \& B$ ?

# 16.3 EXECUTION OF INSTRUCTIONS, MACRO AND MICRO OPERATIONS

In a computer, execution of instructions is carried through macro operations which again can be subdivided into micro operations. In this section, we first define the macro operations that we want to be executed in the computer we are designing. Next, we'll discuss micro operations necessary to execute each macro operation and it will be expressed through RTL. Remember that we have assigned only 3-bits as opcode and hence we can define  $2^3 = 8$  instructions or macro operations with them. Table 16.1 lists all the instructions, corresponding mnemonics (easy to remember short forms), opcodes and 3-to-8 decoder (ID) output when IR is loaded with this opcode.

## **Table 16.1**

#### Instruction Set for the Simple Computer

| Macro operation performed                                                                             | Instruction<br>mnemonic | Opcode                                       | Instruction decoder (ID) output activated |

|-------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------|-------------------------------------------|

| Load data from a specified memory location to ACC                                                     | LDA                     | 000                                          | $D_{0}$                                   |

| Store ACC data in a specified memory location                                                         | STA                     | 0 0 1                                        | $D_{_1}$                                  |

| Halts execution of the program                                                                        | HLT                     | 010                                          | D,                                        |

| Perform bitwise AND operation of ACC with data of a specified memory location and store result in ACC | AND                     |                                              | $D_3$                                     |

| Perform bitwise NOT operation of ACC                                                                  | NOT                     | 100                                          | $D_4$                                     |

| Perform 1-bit left shift of $ACC$ with $ACC[0] \leftarrow 0$                                          | SHL                     | 101                                          | $D_{\mathfrak{s}}$                        |

| Perform addition operation of ACC with data of a specified memory location and store result in ACC    | ADD                     | 110<br>14 (10) (10) (10)<br>1 (10) (10) (10) | $D_{_{6}}$                                |

| Subtract from ACC, data of a specified memory location and store result in ACC                        | SUB                     |                                              | $D_{\gamma}$                              |

## **Instruction Cycles**

To carry out each instruction or macro operation the computer has to go through three distinct phases or cycles. In fetch cycle it brings the instruction or opcode from the program memory. In decoding phase it decodes the opcode and finally the execution is done in execute cycle. These cycles together known as instruction cycle are again repeated for next instruction. It is understandable that fetch and decode phase will be same for all instructions in our simple computer as we have only single byte directly addressed instructions. However, the execution cycle will be different for different instructions depending on the tasks the instruction wants to perform.

#### **Fetch Cycle**

An instruction cycle begins with fetch cycle when TC is reset to 0. Then, only  $T_0$  output of TSD will be high and rest low. As told before PC contains the address of the location from which next instruction is to be fetched, content of PC is loaded into MAR in  $T_0$ .

At the next trigger of master clock TC is incremented by 1 so that  $T_1$  becomes high and other outputs of TSD are low. In this clock cycle, content of memory from location specified by MAR (through 5-to-32 address decoder attached to memory) is loaded to MDR. PC now can be incremented to point to address of next location in program memory, which stores next instruction.

In the next clock cycle TC generates  $T_2 = 1$  when opcode from 3 MSB of MDR is transferred to IR and 5 LSB to MAR. Content of IR is used for decoding opcode in decode phase. Content of MAR will be useful in execute phase if the opcode makes some memory reference, the address of which remain available at MAR. In RTL the above operations can be represented as

$$T_0: MAR \leftarrow PC$$

$T_1: MDR \leftarrow M[MAR], PC \leftarrow PC+1$

$T_2: IR \leftarrow MDR[7:5], MAR \leftarrow MDR[4:0]$

## **Decode Cycle**

In decode cycle we decode the opcode fetched from program memory. Since at  $T_2$ , register IR is loaded with opcode and 3-to-8 decoder (ID) that decodes the opcode is a combinatorial circuit, we finish decoding in  $T_2$  itself. In RTL we express it as

$$T_2: D_0 \dots D_7 \leftarrow \text{DECODE}(IR)$$

Often, the 3rd statement of previously mentioned fetch cycle that loads IR with new opcode is considered a part of decode cycle or fetch-decode together is called fetch cycle.

#### **Execute Cycle**

Micro operations for each instruction are different and we list them first and then give the explanation.

| LDA | $D_0T_3: MDR \leftarrow M[MAR]$                                             |

|-----|-----------------------------------------------------------------------------|

|     | $D_0T_4:ACC \leftarrow MDR, TC \leftarrow 0$                                |

| STA | $D_1T_3: MDR \leftarrow ACC$                                                |

|     | $D_1T_4: M[MAR] \leftarrow MDR, TC \leftarrow 0$                            |

| HLT | $D_2T_3: S \leftarrow 1, TC \leftarrow 0$                                   |

| AND | $D_3T_3: MDR \leftarrow M[MAR]$                                             |

|     | $D_3T_4:ACC \leftarrow ACC \& MDR \ TC \leftarrow 0$                        |

| NOT | $D_4T_3:ACC \leftarrow ACC', \ TC \leftarrow 0$                             |

| SHL | $D_5T_3:ACC[7:1] \leftarrow ACC[6:0], ACC[0] \leftarrow 0, TC \leftarrow 0$ |

| ADD | $D_6T_3: MDR \leftarrow M[MAR]$                                             |

|     | $D_6T_4:ACC \leftarrow ACC + MDR, \ TC \leftarrow 0$                        |

| SUB | $D_7T_3: MDR \leftarrow M[MAR]$                                             |

|     | $D_{7}T_{4}: ACC \leftarrow ACC - MDR, TC \leftarrow 0$                     |

A quick overview of the above list shows, at the completion of each instruction cycle (fetch-decode-execute) TC is reset by which the computer goes to  $T_0$  state and fetch cycle for next instruction begins. Note that, a detailed discussion on execution of the program at register level for every clock trigger appears in Section 16.5.

In operations like LDA, AND, ADD, SUB data is brought from memory, address of which is available in MAR. In executing STA the MAR content denotes the location where data is to be stored in memory.

Macro operations AND, NOT, ADD, SUB use ALU. When HLT is executed S flag is set which stops execution of the program. This flag is cleared through power-on-reset.

Now let's pick up one macro operation (say, LDA) and see how it gets executed through its constituent micro operations. From Table 16.1 we find instruction LDA transfers content of a specified memory location to ACC. If the opcode fetched in fetch cycle is 000 it refers to LDA operation. In decode phase, opcode 000 makes  $D_0 = 1$  and the other outputs of ID are all zero. This is so till IR is refreshed or receives another opcode in the next fetch cycle, state  $T_2$ . Till then  $D_0$  gives output 1.

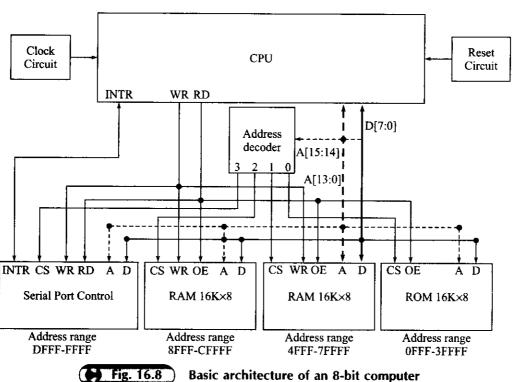

The computer enters execution phase at state  $T_1(T_3 = 1)$ . Now as  $D_0 = 1$ , condition  $D_0T_3 = 1$  and data is read from memory and loaded in MDR. Note that, the address of memory location from which data is to be brought was made available to MAR in state  $T_2$ . Also note that, memory content cannot directly be loaded into ACC (refer to data path shown in Fig. 16.8) and is to be done through MDR. In next clock cycle, i.e. when  $D_0T_4 = 1$  the content of MDR is transferred to ACC via BUS and the macro operation is complete. We reset TC and let the computer begin a new instruction cycle. This analysis can be extended to explain execution of other instructions

At this point we make an important observation that all the instruction executions are completed within 5 clock cycles ( $T_0$  to  $T_4$ ) and hence a 3-bit counter, which can count up to 8 is sufficient as TC in our simple computer.

- 7. What is a fetch cycle?

- 8. Why TC is reset every time an instruction is executed?

## 16.4 DESIGN OF CONTROL UNIT

The control unit is primarily a combinatorial circuit that supplies necessary controls inputs to all the important hardware elements of the computer. This takes timing information from computer master clock and is thus responsible for providing necessary timing and control information. The path through which these signals travel to reach different parts of a computer is called control path. Often we assign a group of wires, called control bus as shared path for this. The control logic is arrived at from (i) basic computer architecture we have adopted in the beginning, (ii) conditions appearing at left hand side of symbol ':' in RTL statements for our simple computer, given in previous section, and (iii) certain other issues, e.g. power-on-reset, control variables need to be activated for intended operation of a particular hardware, etc.

#### **Loading Registers**

Let us first see when parallel load control of IR is to be activated. We find from discussion of previous section, only during  $T_2$  it is loaded. So TSD (Timing counter decoder) output  $T_2$  can be directly connected as parallel load control input of IR. Every time  $T_2$  is active this loads three MSBs of BUS (data path is such, refer to Fig. 16.2), which at that time holds MDR value, into IR. Obviously, at that time BUS selector (BS) should place content of MDR into BUS. This we'll discuss while designing control for BS.

What happens if we allow loading of IR say, in every clock cycle instead of above? Whenever there is some data made available in BUS by any hardware 3 MSB of that will be loaded into IR; ID (decoder) will immediately change and execution corresponding to a different opcode, not the intended one, may begin. You

can understand it'll be all chaos without any sense. Thus we return sanity to our simple machine by loading IR only when opcode is fetched, i.e. in  $T_2$  and we can write logic relation

$$LOAD_{IR} = T_2$$

We see, MDR is loaded during  $T_1$ ,  $D_0T_3$ ,  $D_1T_3$ ,  $D_3T_3$ ,  $D_6T_3$ ,  $D_7T_3$  and corresponding condition is

$$LOAD_{MDR} = T_1 + (D_0 + D_1 + D_3 + D_6 + D_7)T_3$$

Proceeding in same manner we can write, LOAD<sub>MAR</sub> =  $T_0 + T_2$  and

$$LOAD_{4CC} = D_4T_3 + (D_0 + D_3 + D_6 + D_7)T_4$$

## Memory Read/Write

Memory read signal is invoked by:

$$READ_{M} = T_{1} + (D_{0} + D_{3} + D_{6} + D_{7})T_{3}$$

Memory write signal is invoked by:

$$WRITE_{M} = D_{1}T_{A}$$

#### **ALU Control**

Control variables of ALU activated for addition:

$$ALU_{ADD} = D_6 T_4$$

Control variables of ALU activated for subtraction:

$$\mathbf{ALU}_{\mathrm{SUB}} = D_{7}T_{4}$$

Control variables of ALU activated for logic AND:

$$ALU_{AND} = D_3 T_4$$

Control variables of ALU activated for logic NOT:

$$ALU_{NOT} = D_4 T_3$$

## **BUS Controller**

BUS controller gives access

$$BUS_{ACC} = D_1 T_3,$$

to ALU by

$$BUS_{pc} = T_0$$

$$BUS_{MDP} = T_2 + D_0 T_4$$

and

$$BUS_{ALU} = D_4 T_3 + (D_3 + D_6 + D_7) T_4$$

Thus, selection inputs of eight 4-to-1 multiplexers that places data from one of these four devices ACC, PC, MDR and ALU on BUS should become active when corresponding conditions mentioned by above logic equations are met.

#### Other Control Signal

The condition for setting START/STOP flag S is:

$SET_s = D_s T_s [S \text{ is power on reset}]$

The condition for shift left operation of ACC is:

SHIFT\_LEFT\_ $ACC = D_5T_3$

The signal that triggers increment of PC:

$\frac{1}{1}$  INCREMENT<sub>PC</sub> =  $T_1$

Timing counter TC is synchronously reset by:

RESET<sub>TC</sub> =  $(D_2 + D_4 + D_5) T_3 + (D_0 + D_1 + D_3)$

$$+D_6+D_7)T_4$$

Finally, the master clock remains enabled if flag S is not set. Thus  $ENABLE_{CLOCK} = S'$

Based on these equations the control unit of our simple computer can be made. We show the control circuit of ACC, TC and TSD, BS in following three examples. Refer to problems of Section 4 of this chapter for more circuits. Together they make the control unit of our simple computer.

## Example 16.3

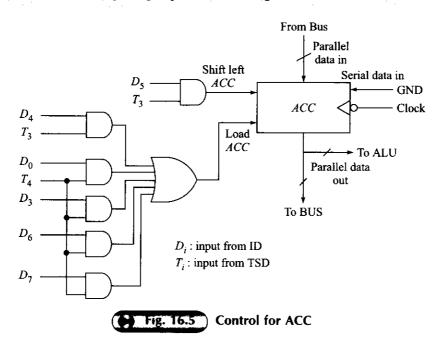

Show using circuit diagrams the control inputs to ACC.

Solution The parallel load shift register ACC in the simple computer designed shifts data to left while serial data in is 0 (GND). It also loads parallel data from BUS. The conditions for these two operations are shown above in the form of logic equations. The corresponding diagram is shown in Fig. 16.5.

## Example 16.4

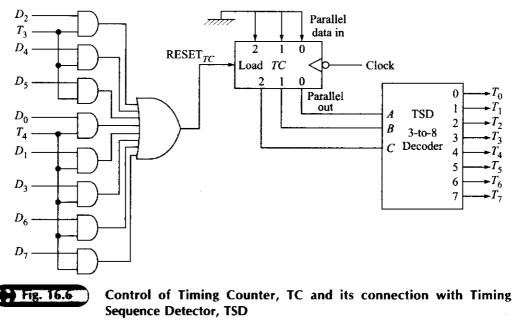

Show using diagrams control inputs to TC and its connection to TSD.

Solution. The timing counter TC is a mod-8 up counter with parallel load facility. When RESET<sub>rc</sub> is activated according to countrol logic discussed in this section, 000 is synchronously loaded and up count resumes. The required circuit diagram is shown in Fig. 16.6.

## Example 16.5

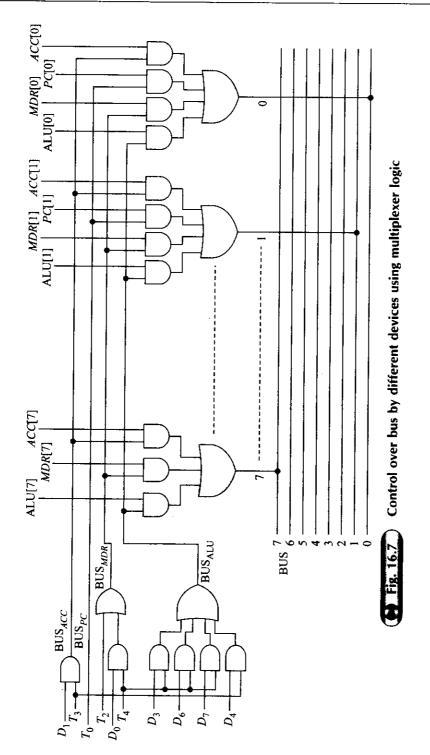

Show using diagram how bus controller works.

Solution The controller developed from control equations discussed in this section is shown in Fig. 16.7. This is developed on multiplexer logic like Fig. 4.5 of Chapter 5. A tri-state bus control can also be designed similar to diagram shown in Fig. 14.26 of Chapter 14. There the DISABLE control input will be fed by complement of respective BUS activate signal, i.e. complement of BUS<sub>ACC</sub>, BUS<sub>ACC</sub>, BUS<sub>ACC</sub>, BUS<sub>ACC</sub>

Note that, PC does not access bit 5 to 7 of BUS as it has only 5 bit binary information that is transferred to MAR via bit 0 to 4 of the BUS. Hence, for 3 MSB there is one AND gate less and the OR gate is of 3 input.

(SELETEST)

- 9. How long instruction decoder outputs  $D_1 \dots D_n$  remain constant?

- 10. What are the instructions of this simple computer in which ALU places data on BUS?

- 11. Which instruction sets flag F?

## 16.5 PROGRAMMING COMPUTER

Now that our simple computer is ready with hardware and instruction sets let us see what computer program can solve the problem with which we started designing our simple machine. In Table 16.2 we present the program in mnemonics along with comments on job done by each instruction. Program in binary code as exists in  $32 \times 8$  memory module will be shown after that.

Thus we need 14 instructions (Table 16.2), all single byte to solve the problem in our simple computer. We need 12 memory locations for storing numbers. So 14 + 12 = 26 bytes of our 32 byte memory are used for this problem. For bigger sized problems we need bigger memory and for more complex problem additional instruction sets and, of course, more complex computer architecture.

Now let us see how program and data remain stored in memory in binary numbers. We know that due to power-on-reset PC is always initialized with 00000, the first location of the memory (Refer Table 16.3) where first instruction of the program is to be stored. We use first 14 locations (address 00000 to 01101) of memory to store instructions. If we store data used in the program, i.e. 11 numbers in next consecutive locations then addresses 01110 to 11000 get filled. The location 11001, i.e. 26th location of memory can be used to store the result. Note that, multiplication is achieved by left shifting ACC and thus we don't need to store any multiplicand for that. If the 10 numbers to be added are say, 5, 2, 1, 3, 8, 6, 5, 2, 7, 4 and the number

## **Table 16.2**

#### Program to Solve Given Problem with Comments

| Instruction<br>Number | Instruction pnemonic | Comment                                    |                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|----------------------|--------------------------------------------|------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | LDA addr1            | loads 1st number to ACC, the address       | of which follows             | opcode           | Tarihi di Mariji da Mariji ya Mariji |

| 2                     | ADD addr2            | fetches 2nd number from memory and         | adds to 1st, store           | s the sum in A   | ICC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                     | ADD addr3            | similarly adds 3rd number                  |                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4                     | ADD addr4            | adds 4th number                            |                              | e partiri        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5                     | ADD addr5            | adds 5th number                            |                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6                     | ADD addr6            | adds 6th number                            |                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7                     | ADD addr7            | adds 7th number                            |                              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| # <b>8</b> * * * * *  | ADD addr8            | adds 8th number                            | ji see i je                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| · 29 a                | ADD addr9            | adds 9th number                            |                              | et farena 11.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10                    | ADD addr10           | adds 10th number, now sum of 10 num        | nbers remain avail           | able in ACC      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| an <b>H</b> ala as    | SUB addr11           | fetches 11th no. from memory, subtract ACC | and the second second second |                  | s result in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12                    | SHL                  | shifts ACC to left by 1 bit, equivalent    | to multiplication b          | y 2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13                    | STA addr 12          | stores content of ACC in memory in th      | <b>-</b>                     |                  | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14                    | HTL                  | halts the computer                         |                              | # 1.<br><br>:30= |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

subtracted is say, 9 then we can fill up first 25 locations of memory as shown in Fig. 16.14. The 26th location, before the program is run, may contain anything but after the program is run will contain the end result, i.e. 68 expressed in binary. Memory content is often shown in hexadecimal instead of binary. Refer to Problems 16.19 and 16.20 for this.

## **Program Execution**

Now let us see how the program gets executed in first few instruction cycles. We note the change in the value of the registers along with ID and TSD in each clock cycle since the program begins. Table 16.4 shows sequential progress of our simple computer with every trigger of system clock. As told before *PC*, *TC* and *S* are power on reset. They all contain zero in the beginning when the computer is switched on.

In first clock cycle, the machine is in  $T_0$  state given by TSD that decodes TC. At  $T_0$ , content of PC that contains the starting address of the program is copied to MAR. Corresponding micro operation is shown in rightmost column of Table 16.4. TC is incremented by 1.

In next clock cycle, TC and PC are incremented by 1, data from memory is loaded to MDR that contains the first instruction.

In  $3^{\rm rd}$  clock cycle TC is incremented, IR gets the opcode and MAR gets address for first data. Note that decoding of IR is also done in same clock cycle that makes  $D_0$  high, as opcode is 000 (LDA). This completes the fetch cycle, which is common for all instructions.

In executing LDA instruction the first state is  $T_3$  state. Here, data from 15th location of Memory (MAR = 01110) which contains 00000101, decimal equivalent of 5 is loaded to MDR. In  $T_4$  state this data is transferred to ACC and macro operation LDA is fully executed. This completes the first instruction cycle. Note that timing counter (TC) is to be reset after execution of data transfer from MDR to ACC and that begins the next instruction fetch.

## **Table 16.3**

## Program and Data Section of the Memory

|          | •         |          | <b>Q</b> ,                                                                       |

|----------|-----------|----------|----------------------------------------------------------------------------------|

| Memory   | Memory    | Memory   |                                                                                  |

| location | address   | content  | Comment                                                                          |

| number   | in binary |          |                                                                                  |

| 1        | 00000     | 00001110 | Program section begins. Loads 1st no. from location 01110 to ACC. 3MSB 000: Load |

| 2        | 00001     | 11001111 | 3MSB110: ADD, 5LSB 01111: Address of 2nd operand                                 |

| 3        | 00010     | 11010000 | •                                                                                |

| 4        | 00011     | 11010001 | •                                                                                |

| 5        | 00100     | 11010010 | •                                                                                |

| 6        | 00101     | 11010011 | First 14 locations, i.e. memory address 00000 to 01101 contain instructions.     |

| 7        | 00110     | 11010100 | Here, three MSBs always refer to opcode. Five LSBs refer to memory               |

| 8        | 00111     | 11010101 | address for instructions LDA, ADD, SUB, STA. For instructions                    |

| 9        | 01000     | 11010110 | SHL and HLT, five LSBs can be anything as they are not referred                  |

| 10       | 01001     | 11010111 | anywhere.                                                                        |

| 11       | 01010     | 11111000 | •                                                                                |

| 12       | 01011     | 10100000 | •                                                                                |

| 13       | 01100     | 00111001 |                                                                                  |

| 14       | 01101     | 01000000 | Halts computer. Program section ends.                                            |

| 15       | 01110     | 00000101 | The data section starts. Stores 1st number, 5 expressed in binary                |

| 16       | 01111     | 00000010 | 2nd no. 2 in binary                                                              |

| 17       | 10000     | 00000001 |                                                                                  |

| 18       | 10001     | 00000011 |                                                                                  |

| 19       | 10010     | 00001000 |                                                                                  |

| 20       | 10011     | 00000110 |                                                                                  |

| 21       | 10100     | 00000101 |                                                                                  |

| 22       | 10101     | 00000010 |                                                                                  |

| 23       | 10110     | 00000111 |                                                                                  |

| 24       | 10111     | 00000100 |                                                                                  |

| 25       | 11000     | 00001001 | Stores 11th number, 9 that is subtracted from the sum of 10 nos.                 |

| 26       | 11001     | xxxxxxx  | After the program is run it becomes 01000100, i.e. 68 in decimal.                |

| 27       | 11010     | xxxxxxx  | UNUSED                                                                           |

| 28       | 11011     | XXXXXXX  | UNUSED                                                                           |

| 29       | 11100     | XXXXXXX  | UNUSED                                                                           |

| 30 34.   | 11101     | XXXXXXX  | UNUSED                                                                           |

| 31       | 11110     | XXXXXXX  | UNUSED                                                                           |

| 32       | 11111     | XXXXXXXX | UNUSED                                                                           |

The fetch cycle is repeated in clock cycle 6 to 8. Since the instruction fetched is ADD (opcode 110) corresponding micro operations are performed in clock cycles 9 and 10 followed by next instruction fetch, starting again at 11th clock cycle. This continues till we reach 14th instruction HLT which when executed, sets S flag. This inhibits the system clock output in our design; thus content of all registers and memory will remain unchanged after that till the computer is switched off.

## Table 16.4 Execution of the Program at Register Level

| Clock<br>Cycle | TC\$ | TSD         | PC\$  | MAR   | MDR      | IR  | ID                         | ACC      | S   | Micro operation performed<br>after clock trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |